Dibuat Oleh :

Dibuat Oleh :-Bayu f -Jalil -Aris

RISA(REDUCED INSTRUCTIONS SET ARSITECTURE) :

Dibuat Oleh :-Bayu f -Jalil -Aris

PERBEDAAN RISC DAN CISC

Dibuat Oleh :-Bayu f -Jalil -Aris

RISC (Reduced Instruction Set Computer)

Dibuat Oleh :-Bayu f -Jalil -Aris

Selasa, 01 Desember 2015

Jumat, 27 November 2015

1. REDUCED INSTRUCTIONS SET ARSITECTURE

REDUCED INSTRUCTIONS SET ARCHITECTURE

Instruction Set Architecture (ISA) adalah “atribut dari sistem komputasi yang dilihat dari sudut pandang programmer, seperti struktur konseptual, perilaku fungsional yang diterapkan pada organisasi aliran data dan kendali atas desain logika dan implementasi fisik pada mesin. -Amdahl, Blaaw, and Brooks, 1964.” Dengan kata lain, ISA meliputi spesifikasi yang menentukan bagaimana programmer bahasa mesin akan berinteraksi dengan komputer. ISA menentukan sifat komputasional komputer.

Selain itu ISA menjadi penghubung antar muka antara software dan hardware. Dan juga menyediakan mekanisme agar software bisa bekerja optimal dengan hardware yang tersedia.

ISA terdiri dari:

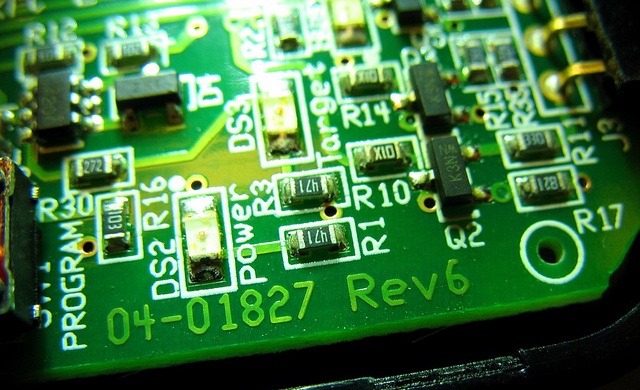

1.Organisasi penyimpanan yang dapat diprogram(Programmable Storage)

2.Tipe Data & struktur Data : Encoding & Representasi

3.Set Instruksi

4.Format Instruksi

5.Mode pengalamatan (Addressing) dan mode akses data danakses intruksi.

Instruksi Set Arsitektur dihitung berdasarkan pada:

- Banyaknya ruang memori utama yang digunakan oleh program.

- Kerumitan instruksi.

- Panjang instruksi dalam bits.

- Jumlah total instruksi pada set instruksi.

Contoh Implementasi ISA

• Bahasa pemrograman Java adalah bahasa interprentasi yang menjalankan sebuah mesin software Java Virtual Machine (JVM).

• Sebuah JVM ditulis menggunakan bahasa asli untuk prosesor dengan array yang luas, termasuk MIPS dan Intel.

• Seperti mesin yang nyata, JVM memiliki Instructure Set Architecture nya sendiri yang disebut Bytecode. ISA ini didesain untuk kompatibel dengan arsitektur dari berbagai macam mesin dimana JVM dijalankan.

• Java bytecode adalah bahasa berbasis stack.

• Kebanyakan instruksi instruksi dengan ero address.

• JVM memiliki 4 register yang menyediakan akses pada 5 region dari memori utama.

• Java di desain untuk platform interoperability, bukan performa

2. PERBEDAAN RISC DAN CISC

Complex Instruction Set Computing (CISC) atau kumpulan instruksi komputasi kompleks. Adalah suatu arsitektur komputer dimana setiap instruksi akan menjalankan beberapa operasi tingkat rendah, seperti pengambilan dari memori (load), operasi aritmatika, dan penyimpanan ke dalam memori (store) yang saling bekerja sama.

Tujuan utama dari arsitektur CISC adalah melaksanakan suatu instruksi cukup dengan beberapa baris bahasa mesin yang relatif pendek sehingga implikasinya hanya sedikit saja RAM yang digunakan untuk menyimpan instruksi-instruksi tersebut. Arsitektur CISC menekankan pada perangkat keras karena filosofi dari arsitektur CISC yaitu bagaimana memindahkan kerumitan perangkat lunak ke dalam perangkat keras.

Karakteristik CISC

- Sarat informasi memberikan keuntungan di mana ukuran program-program yang dihasilkan akan menjadi relatif lebih kecil, dan penggunaan memory akan semakin berkurang. Karena CISC inilah biaya pembuatan komputer pada saat itu (tahun 1960) menjadi jauh lebih hemat.

- Dimaksudkan untuk meminimumkan jumlah perintah yang diperlukan untuk mengerjakan pekerjaan yang diberikan. (Jumlah perintah sedikit tetapi rumit) Konsep CISC menjadikan mesin mudah untuk diprogram dalam bahasa rakitan.

Ciri-ciri

- Jumlah instruksi banyak

- Banyak terdapat perintah bahasa mesin

- Instruksi lebih kompleks

- Pengaplikasian CISC yaitu pada AMD dan Intel.

B.

RISC (Reduced Instruction Set Computer)

RISC

singkatan dari Reduced Instruction Set Computer. Merupakan bagian

dari arsitektur mikroprosessor, berbentuk kecil dan berfungsi untuk

negeset istruksi dalam komunikasi diantara arsitektur yang lainnya.

Sejarah

RISC

Proyek

RISC pertama dibuat oleh IBM, stanford dan UC –Berkeley pada akhir

tahun 70 dan awal tahun 80an. IBM 801, Stanford MIPS, dan Barkeley

RISC 1 dan 2 dibuat dengan konsep yang sama sehingga dikenal sebagai

RISC.

RISC

mempunyai karakteristik:

- One cycle execution time : satu putaran eksekusi. Prosessor RISC mempunyai CPI (clock per instruction) atau waktu per instruksi untuk setiap putaran. Hal ini dimaksud untuk mengoptimalkan setiap instruksi pada CPU.

- Pipelining:adalah sebuah teknik yang memungkinkan dapat melakukan eksekusi secara simultan.Sehingga proses instruksi lebih efiisien

- Large number of registers: Jumlah register yang sangat banyak. RISC di Desain dimaksudkan untuk dapat menampung jumlah register yang sangat banyak untuk mengantisipasi agar tidak terjadi interaksi yang berlebih dengan memory.

Ciri-ciri

- Instruksi berukuran tunggal

- Ukuran yang umum adalah 4 byte

- Jumlah pengalamatan data sedikit,

- Tidak terdapat pengalamatan tak langsung

- Tidak terdapat operasi yang menggabungkan operasi load/store dengan operasi aritmatika

- Tidak terdapat lebih dari satu operand beralamat memori per instruksi

- Tidak mendukung perataan sembarang bagi data untuk operasi load/ store.

- Jumlah maksimum pemakaian memori manajemen bagi suatu alamat data adalah sebuah instruksi .

3. RISC (Reduced Instruction Set Computer)

Lebih Jauh Tentang RISC

RISC singkatan dari Reduced Instruction Set Computer. Merupakan bagian dari arsitektur mikroprosessor, berbentuk kecil dan berfungsi untuk negeset istruksi dalam komunikasi diantara arsitektur yang lainnya.

Sejarah RISC

Proyek RISC pertama dibuat oleh IBM, stanford dan UC –Berkeley pada akhir tahun 70 dan awal tahun 80an. IBM 801, Stanford MIPS, dan Barkeley RISC 1 dan 2 dibuat dengan konsep yang sama sehingga dikenal sebagai RISC.

RISC mempunyai karakteristik :

One cycle execution time :

satu putaran eksekusi. Prosessor RISC mempunyai CPI (clock per instruction) atau waktu per instruksi untuk setiap putaran. Hal ini dimaksud untuk mengoptimalkan setiap instruksi pada CPU.

Pipelining:

adalah sebuah teknik yang memungkinkan dapat melakukan eksekusi secara simultan.Sehingga proses instruksi lebih efiisien

Large number of registers:

Jumlah register yang sangat banyak. RISC di Desain dimaksudkan untuk dapat menampung jumlah register yang sangat banyak untuk mengantisipasi agar tidak terjadi interaksi yang berlebih dengan memory.

Ciri-ciri:

- Instruksi berukuran tunggal

- Ukuran yang umum adalah 4 byte

- Jumlah pengalamatan data sedikit,

- Tidak terdapat pengalamatan tak langsung

- Tidak terdapat operasi yang menggabungkan operasi load/store dengan operasi aritmatika

- Tidak terdapat lebih dari satu operand beralamat memori per instruksi

- Tidak mendukung perataan sembarang bagi data untuk operasi load/ store.

- Jumlah maksimum pemakaian memori manajemen bagi suatu alamat data adalah sebuah instruksi.

PERBANDINGAN CISC DAN RISC

Tujuan utama dari arsitektur CISC adalah untuk menyelesaikan tugas beberapa baris perakitan dalam sebuah arsitektur. Hal ini dicapai dengan membangun prosesor hardware yang mampu memahami dan menjalankan beberapa rangkaian operasi. Kita bisa mengukur perbedaan antara RISC dan CISC menggunakan dasar persamaan kinerja komputer sebagai berikut:

Kinerja komputer, yang diukur oleh lama eksekusi program, berbanding lurus Untuk waku siklus, jumlah siklus clock per instruksi, dan jumlah instruksi dalam program ini. Memperpendek siklus clock, bila mungkin, menghasilkan peningkatan kinerja RISC serta CISC. Jika tidak, mesin CISC meningkatkan kinerja dengan mengurangi jumlah nomor instruksi program. Komputer RISC meminimalkan jumlah siklus per instruksi. Namun kedua arsitektur dapat menghasilkan hasil yang identik dalam jumlah waktu yang sama. Pada level gate, kedua sistem melakukan kuantitas setara dengan pekerjaan.

Mesin CISC mengandalkan microcode untuk mengatasi kompleksitas instruksi. Microcode memberitahu prosesor bagaimana melaksanakan setiap instruksi. Untuk alasan kinerja, microcode bersifat kompak, efisien, dan tentu saja harus benar.

Bagaimanapun instruksi microcode dibatasi oleh instruksi panjang variabel, yang memperlambat proses decoding, dan berbagai jumlah siklus clock per instruksi yang membuatnya sulit untuk melaksanakan instruksi pipeline. Proses translasi tambahan akan membutuhkan waktu. Semakin kompleks set instruksi, semakin banyak waktu yang dibutuhkan untuk mencari instruksi dan melibatkan perangkat keras yang cocok untuk pelaksanaannya.

Arsitektur RISC mengambil pendekatan yang berbeda. Kebanyakan instruksi RISC mengeksekusi dalam satu siklus clock. Untuk mencapai kecepatan ini, kontrol microprogrammed digantikan oleh kontrol terprogram, yang lebih cepat di mengeksekusi instruksi. Ini membuatnya lebih mudah untuk melakukan instruksi pipelining, tetapi lebih sulit untuk berurusan dengan kompleksitas pada tingkat hardware. Dalam sistem RISC, kompleksitas dihapus dari set instruksi didorong naik tingkat ke domain dari compiler.

Mesin CISC mengandalkan microcode untuk mengatasi kompleksitas instruksi. Microcode memberitahu prosesor bagaimana melaksanakan setiap instruksi. Untuk alasan kinerja, microcode bersifat kompak, efisien, dan tentu saja harus benar.

Bagaimanapun instruksi microcode dibatasi oleh instruksi panjang variabel, yang memperlambat proses decoding, dan berbagai jumlah siklus clock per instruksi yang membuatnya sulit untuk melaksanakan instruksi pipeline. Proses translasi tambahan akan membutuhkan waktu. Semakin kompleks set instruksi, semakin banyak waktu yang dibutuhkan untuk mencari instruksi dan melibatkan perangkat keras yang cocok untuk pelaksanaannya.

Arsitektur RISC mengambil pendekatan yang berbeda. Kebanyakan instruksi RISC mengeksekusi dalam satu siklus clock. Untuk mencapai kecepatan ini, kontrol microprogrammed digantikan oleh kontrol terprogram, yang lebih cepat di mengeksekusi instruksi. Ini membuatnya lebih mudah untuk melakukan instruksi pipelining, tetapi lebih sulit untuk berurusan dengan kompleksitas pada tingkat hardware. Dalam sistem RISC, kompleksitas dihapus dari set instruksi didorong naik tingkat ke domain dari compiler.

CISC

|

RISC

|

Kompleks pada microcode

|

Kompleks pada compiler

|

Penekanan pada perangkat keras

|

Penekanan pada perangkat lunak

|

Termasuk instruksi kompleks multi-clock

|

Single-clock, hanya sejumlah kecil instruksi

|

Memori-ke-memori: “LOAD” dan “STORE”

saling bekerjasama |

Register ke register: “LOAD” dan “STORE”

adalah instruksi2 terpisah |

Ukuran kode kecil, kecepatan rendah

|

Ukuran kode besar, kecepatan (relatif) tinggi

|

Transistor digunakan untuk menyimpan instruksi2 kompleks

|

Transistor banyak dipakai untuk register memo

|

Mode pengalamatan Banyak

|

Mode pengalamatan sedikit

|

Panjang Instruksi yang variatif

|

Panjang instruksi yang tetap

|

Pendekatan CISC bertujuan untuk meminimalkan jumlah instruksi per program, dengan cara mengorbankan kecepatan eksekusi sekian siklus/detik. Sedangkan RISC bertolak belakang, tujuannya mengurangi jumlah siklus/detik setiap instruksi dibayar dengan bertambahnya jumlah instruksi per program.

Perbedaan RISC dengan CISC dilihat dari segi instruksinya

RISC ( Reduced Instruction Set Computer )

- Menekankan pada perangkat lunak, dengan sedikit transistor

- Instruksi sederhana bahkan single

- Load / Store atau memory ke memory bekerja terpisah

- Ukuran kode besar dan kecapatan lebih tinggi

- Transistor didalamnya lebih untuk meregister memori

CISC ( Complex Instruction Set Computer )

- Lebih menekankan pada perangkat keras, sesuai dengan takdirnya untuk pragramer.

- Memiliki instruksi komplek. Load / Store atau Memori ke Memori bekerjasama

- Memiliki ukuran kode yang kecil dan kecepatan yang rendah.

- Transistor di dalamnya digunakan untuk menyimpan instruksi – instruksi bersifat komplek.

Contoh-contoh RISC dan CISC:

RISC :

1. Komputer vektor

2. Mikroprosesor Intel 960

3. Itanium (IA64) dari Intel Corporation

4. Power PC dari International Business Machine, dll.

CISC :

1. Prosesor system/360

2. Prosesor VAX

3. Prosesor PDP-11

4. CPU AMD

5. Intel x86, dll.

KESIMPULAN

C. KESIMPULAN

Rancangan RISC dapat memperoleh keuntungan dengan mengambil sejumlah feature CISC dan Rancangan CISC dapat memperoleh keuntungan dengan mengambil sejumlah feature RISC. Hasilnya adalah bahwa sejumlah rancangan RISC yang terbaru, yang dikenal sebagai PowerPC, tidak lagi “murni” RISC dan rancangan CISC yang terbaru, yang dikenal sebagai Pentium, memiliki beberapa karakteristik RISC. Sehingga antara RISC dan CISC saling mengisi.

Rancangan RISC dapat memperoleh keuntungan dengan mengambil sejumlah feature CISC dan Rancangan CISC dapat memperoleh keuntungan dengan mengambil sejumlah feature RISC. Hasilnya adalah bahwa sejumlah rancangan RISC yang terbaru, yang dikenal sebagai PowerPC, tidak lagi “murni” RISC dan rancangan CISC yang terbaru, yang dikenal sebagai Pentium, memiliki beberapa karakteristik RISC. Sehingga antara RISC dan CISC saling mengisi.

Terima kasih ^-^

Minggu, 01 November 2015

Daftar Pustaka

Daftar Pustaka

http://jamilah.staff.gunadarma.ac.id/

http://dina_agustin.staff.gunadarma.ac.id

http://widuri.raharja.info/index.php

https://www.cis.upenn.edu

http://www.sdsc.edu

http://www.eecg.toronto.edu/~moshovos/ACA06/lecturenotes/003-ISA.pdf